# Pefformance and Electrical Charactrization of Ge-Nanowire Field Effect Transistor

Sanjeet Kumar Sinha and Sweta Chander

School of Electronics and Electrical Engineering, Lovely Professional University, Phagwara, Punjab, India.

Abstract:- In Nanoscale regime some disadvantages are associated with the existing MOSFETs, nanowire FET devices are one of the alternative semiconductor devices which have potential to replace the existing MOSFET technology in future. In this paper a simulation study is reported that how Ge nanowire FET devices can replace the MOSFETs. In devices metallic contacts are considered as source and drain as well as Ge nanowire is considered as a channel between source and drain. Different simulations are performed in nanoHUB with different channel length to analyze the impact of different factors on electronic transport inside the nanowire FETs. Analysis are observed with the scaling the channel length of the nanowire FETs. It is observed through simulation results that at low gate voltage, drain current and the sub-threshold swing increases.

Keywords: MOSFET, NW-FET, Threshold-voltage, Ge-Nanowire FET.

## I. INTRODUCTION

The bulk process of manufacturing the MOSFET is relatively simple and is widely adopted by the semiconductor industries. According to ITRS device scaling is important factor to achieve the goal of semiconductor industry, but scaling beyond 20 nm is quite complicated to maintain all the device parameter further [1]-[4]. Many efforts are going on parallel to replace the existing MOSFET technology worldwide. In scaling functionality and reliability of the device has to maintain at small dimension, because of this activity short channel length comes into the pictures along with some other parameters. Effect of this causes the reduced sub-threshold swing which further causes to difficulty in turn on the device. In MOSFET (metal oxide semiconductor field effect transistor) technology, generally two device structures are studied widely, the first one is bulk structure and second one is silicon on insulator[5]-12]. In bulk structure any transistor is fabricated directly on the substrate of semiconductor whereas in SOI transistor is fabricated on thin layer of silicon and it is separated with a layer of insulator from the substrate.

## **II. GERMANIUM STRUCTURE**

In nano-regime many devices has capability to replace the existing MOSFET technology but still research are going on for mass production. Ge-Nanowire FET has immerges as a potential candidate for future semiconductor devices. Silicon and Ge are widely available material in the Earth, whereas the crystal of silicon structure is highly stable. Because of good electrical and mechanical properties of Si material it is best suitable for semiconductor industry [13]-18]. SiO2 is a native oxide of Si which is widely used as insulator in the in semiconductor devices.

Fig. 1. Cross view of Ge structure

## III. **RESULT ANALYSIS**

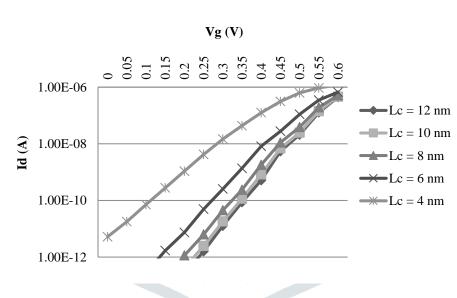

For simulation of Ge nanowire FET device, the length of source and drain are fixed to 10nm and the channel length is in range of 12 to 4 nm. Other parameter like oxide-thickness of the device as well as the diameter of the nanowire are considered as 2.5nm and 1 nm respectively. Doping concentration of 2e+20/cm<sup>3</sup> is considered for donor, source and drain doping concentration, whereas 1e+06/cm<sup>3</sup> is fixed for acceptor, source and donor concentration.

Fig.2. I-V plot for Ge-nanowire FET device

## IV. CONCLUSION

In nanometer regime nanowire FET devices have some promising characteristics which will lead a potential candidate for future semiconductor device. A new class of devices is represented by nanowire FET. This paper is focused to the electronic-transport of Ge nanowire FET with variable channel length. The simulation results shows that while reducing the channel length of the nanowire FET device, a substantial increment in sub-threshold swing and drain current is observed at low gate voltage, which on is very important for nanometer devices.

## REFERENCES

- [1] G. Moore, "Progress in Digital Electronics", IEDM Tech Digest, pp11-13, 1975.

- [2] S.W. Chung, J.-Y. Yu, and J. R. Heath, "Silicon nanowire devices," Appl. Phys. Lett., vol. 76, no. 15, pp. 2068–2070, Apr. 2000.

- [3] C. Thelander, P. Agarwal, S. Brongersma, J. Eymery, L. F. Feiner, A. Forchel, M. Scheffler, W. Riess, B. J. Ohlsson, U. Gösele, and L. Samuelson, "Nanowire-based one-dimensional electronics," *Mater Today*, vol. 9, no. 10, pp. 28–35, Oct. 2006.

- [4] N. Singh, A. Agarwal, L. K. Bera, T. Y. Liow, R. Yang, S. C. Rustagi C. H. Tung, R. Kumar, G. Q. Lo, N. Balasubramanian, and D.-L. Kwong, "High-performance fully depleted silicon nanowire (diameter ≤ 5 nm) gate-all-around CMOS devices," *IEEE Electron Device Lett.*, vol. 27, no. 5, pp. 383–385, May 2006.

- [5] Y. Hu, J. Xiang, G. Liang, H. Yan, and C. M. Lieber, "Sub-100 nanometer channel length Ge/Si nanowire transistors with potential for 2 THz switching speed," *Nano Lett.*, vol. 8, no. 3, pp. 925–930, Mar. 2008.

- [6] J. Guo, J.Wang, E. Polizzi, S. Datta, and M. Lundstrom, "Electrostatics of nanowire transistors," *IEEE Trans. Nanotechnol.*, vol. 2, no. 4, pp. 329-334, Dec. 2003.

- [7] S. Luryi, "Quantum capacitance devices," Applied Physics Letters vol. 52, pp.501-503, 1998.

- [8] D. L. John, L. C. Castro, and D. L. Pulfrey, "Quantum capacitance in nanoscale device modeling," *J. Appl. Phys.*, vol. 96, no. 9, pp. 5180–5184, Nov. 2004.

- [9] S.K.Sinha, S Chaudhury," Impact of Oxide Thickness on Gate Capacitance- A Comprehensive analysis on MOSFEt, nanowire FET, and CNTFET Devices",*IEEE Trans. Nanotechnology*, vol. 12, no. 6, pp. 958-964, November 2013.

- [10] S. Jain, "Measurement of threshold voltage and channel length of submicron MOSFET's," Proc. Inst. Elect. Eng., vol. 135-1, p. 162, 1988.

- [11] K. Terada and H. Muta, "A new method to determine effective MOSFET channel length," Jpn. J. Appl. Phys., vol. 18, p. 953, 1979.

- [12] Y. Taur, Y. J. Mii, R. Logan, and H. S. Wong, "On effective channel length in 0.1\_m MOSFET's," *IEEE Electron Device Lett.*, vol. 16, p. 136, 1995.

- [13] Tsakalakos, P. Losee, J. Balch, A. L. Bogorad, W. J. Taft, J. J. Likar, and R. Herschitz, "Radiation hard silicon nanowire field effect transistors," in *Proc. NANO*, Aug. 18–21, pp. 582–583, 2008.

- [14] Washio, K. "SiGe HBT and BiCMOS technologies for optical transmission and wireless communication systems". *IEEE Transactions on Electron Devices*, volume 50 (3) pp. 656, 2003.

- [15] Teal, Gordon K. "Single Crystals of Germanium and Silicon-Basic to the Transistor and Integrated Circuit". *IEEE Transactions on Electron Devices*. ED-23 (7): 621–639, July 1976.

- [16] Dunwei Wang, Qian Wang, Ali Javey, Ryan Tu, Hongjie Dai, Hyoungsub Kim, Paul C. McIntyre, Tejas rishnamohan and Krishna C. Saraswat, "Germanium nanowire field-effect transistors with SiO2 and high-k HfO2 gate dielectrics", *Applied Physics Letters*, Volume 83, Number 12, September 2003.

- [17] Y. K. Choi, J. Zhu, J. Grunes, J. Bokor, and G. A. Somorjai, "Fabrication of sub-10-nm silicon nanowire arrays by size reduction lithography," *The Jour. of Phy. Chem. B*, Vol. 107(15), pp. 3340-3343, 2003.

- [18] L. Tsakalakos, P. Losee, J. Balch, A. L. Bogorad, W. J. Taft, J. J. Likar, and R. Herschitz, "Radiation hard silicon nanowire field effect transistors," in *Proc. NANO*, pp. 582–583, 2008.